本文共 5713 字,大约阅读时间需要 19 分钟。

记录些设备树相关的规范。

1. 节点, 属性, 值

2. compatible, 匹配/兼容的驱动名称, OpenFirm框架会去寻找相应的驱动

3. 寄存器

amba_apu: amba_apu@0 { compatible = "simple-bus"; #address-cells = <2>; #size-cells = <1>; ranges = <0 0 0 0 0xffffffff>; gic: interrupt-controller@f9010000 { compatible = "arm,gic-400", "arm,cortex-a15-gic"; #interrupt-cells = <3>; reg = <0x0 0xf9010000 0x10000>, <0x0 0xf9020000 0x20000>, <0x0 0xf9040000 0x20000>, <0x0 0xf9060000 0x20000>; interrupt-controller; interrupt-parent = <&gic>; interrupts = <1 9 0xf04>; }; }; address-cells: 地址单元, = 2, 代表reg属性中2个32位数代表一个地址

size-cells: 长度单元, =1, 代表reg属性中1个32位数代表一个长度

4. 中断

还以上述为例,

interrupt-controller, 空键值的属性。代表该节点是一个中断控制器。 是的, gic是一个中断控制器。(包括gpio等, 都可抽象为中断控制器)

interrupt-parent: 由于中断数目众多, 现在多采用树状结构, 即最终到arm core的 irq num 是由各个/各层中断控制器汇总而来。

interrupts: 具体的中断信息, 其中数值代表的含义 跟 其中的interrupt-cells 属性有关。 上述例子中 interrupt-cells = 3, 代表中断由三个数据域组成。 <1(中断域), 9(中断号), 0xf04(触发条件)>

参考/Documentation/devicetree/bindings/interrupt-controller/arm,gic.txt

The 1st cell is the interrupt type; 0 for SPI interrupts, 1 for PPI interrupts. The 2nd cell contains the interrupt number for the interrupt type. SPI interrupts are in the range [0-987]. PPI interrupts are in the range [0-15]. The 3rd cell is the flags, encoded as follows: › bits[3:0] trigger type and level flags. › › 1 = low-to-high edge triggered › › 2 = high-to-low edge triggered (invalid for SPIs) › › 4 = active high level-sensitive › › 8 = active low level-sensitive (invalid for SPIs). › bits[15:8] PPI interrupt cpu mask. Each bit corresponds to each of › the 8 possible cpus attached to the GIC. A bit set to '1' indicated › the interrupt is wired to that CPU. Only valid for PPI interrupts. › Also note that the configurability of PPI interrupts is IMPLEMENTATION › DEFINED and as such not guaranteed to be present (most SoC available › in 2014 seem to ignore the setting of this flag and use the hardware › default value).

故上述 <1 9 0xf04> 含义为:

1号中断域

9号中断号

PPI中断, 绑定cpu0,1,2,3, 高电平有效

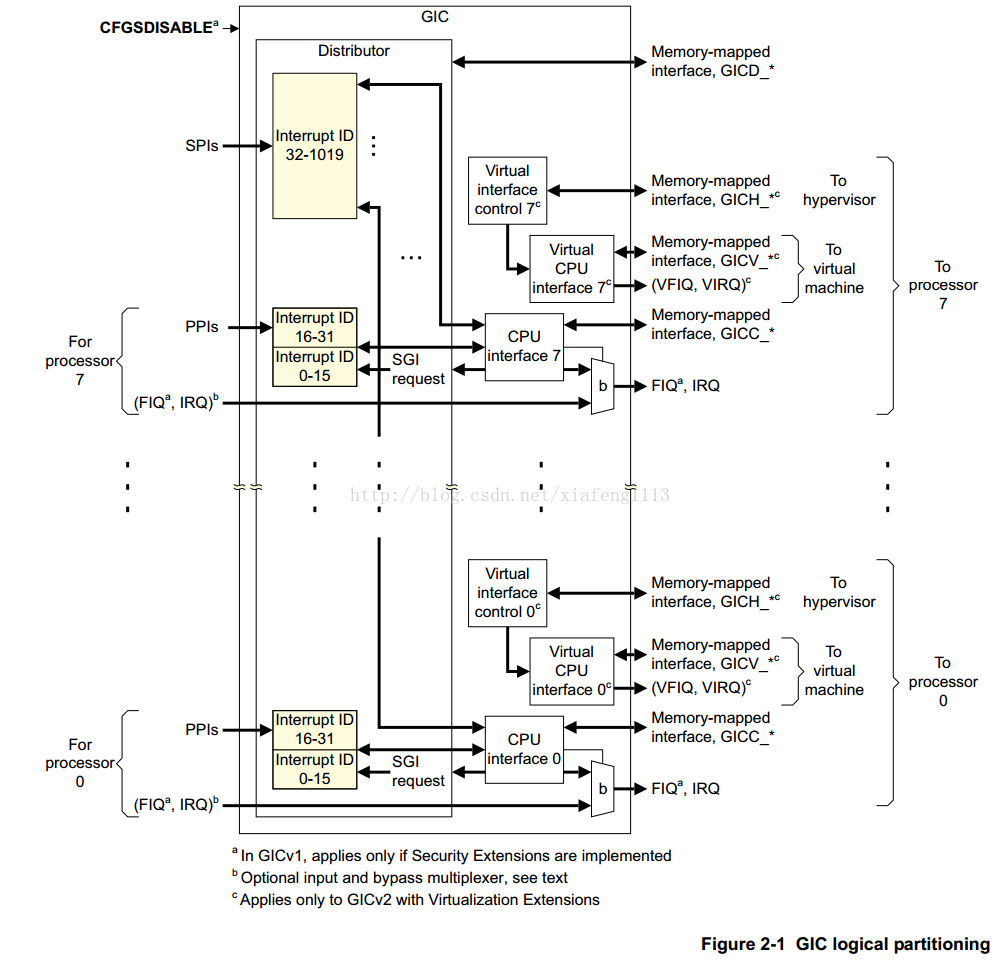

此处记录下ARM架构中断相关。

arm cpu核心有7种异常模式(armv8 多了2种, hypervisor和monitor模式)

跟中断相关的是其中两种, irq和fiq, 对应两根pin。

故外部必然有中断控制器进行拓展并管理。

从中断控制器角度 看 外部来的中断, 常用的可分为3种,

- SGI, Software-Generated Interrupt, 软件中断(不等同于swi), 软件可以通过中断控制器的GICD_SGIR寄存器来触发一个中断事件, 即会触发irq中断。 此类中断可用于多核的核间通信。例如 cpu0 写GICD_SGIR寄存器 触发cpu1 irq。SGI统一编号0~15。

- PPI, Private Peripheral Interrupt, 私有的外设中断, 该PPI只能分配给特定的处理器。统一编号16-31。每个cpu的local timmer即arch timmer产生的中断就是通过PPI发给cpu的。

- SPI, Shared Peripheral Interrupt, 共享的外设中断, 即各个cpu核心都可以收到该中断。 统一编号32~1019。 常见的global timmer, uart, gpio, usb等等外设控制器都通过该中断通知cpu核心。

其他还有虚拟中断和Maintenace interrupt, 暂不讨论。

贴张常见的图